仿真引擎(Simulation engine)

这一章解释了仿真引擎的内部构造。

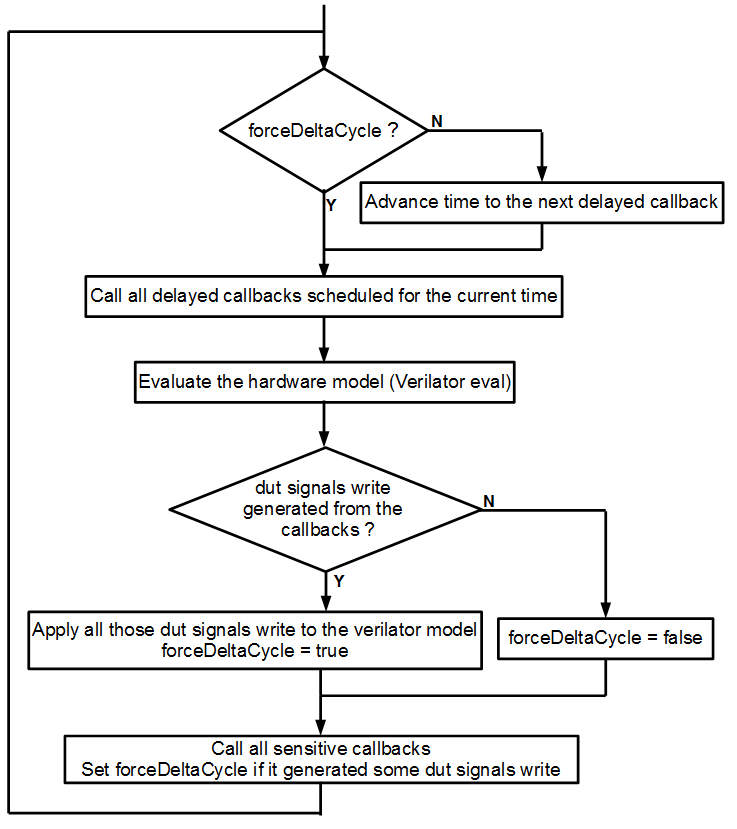

仿真引擎通过在顶层Verilator C++仿真模型中应用以下仿真环来模仿事件驱动的仿真器(像VHDL/Verilog):

在底层, 仿真引擎管理如下原语:

敏感回调, 允许用户在每个仿真增量周期调用函数;

延时回调, 允许用户在未来仿真时间调用函数;

仿真线程, 允许用户描述并行进程;

指令缓存, 允许用户一直延时对DUT的写访问直到当前增量周期;

关于这些原语有一些使用的操作:

敏感回调可以像时钟上升沿一样, 当给定条件发生唤醒仿真线程;

延时回调可以用来调度激励, 例如在给定时间, 或者时钟翻转后取消对复位信号断言;

上述二者均可以用来恢复仿真线程;

仿真线程可以用来产生激励并检查DUT的输出值;

指令缓存的目的主要是避免DUT和testbench之间的并发事件。