中断设计规范(Interrupt Design Spec)

一、IP级中断库(IP level interrupt Factory)

| 寄存器 | 接入类型 | 描述 |

|---|---|---|

| RAW | W1C | 整形原始(raw)寄存器, 通过int设置并且当总线写1时清空 |

| FORCE | RW | 整形force寄存器, 用于SW类型的debug |

| MASK | RW | 整形mask寄存器, 1:关闭, 0:打开;默认为1 |

| STATUS | RO | 整形状态, 只读。status = (raw | | force) && ! mask |

Spinal使用:

busif.interruptFactory("T", io.a, io.b, io.c, io.d, io.e)

二、系统级中断合并(SYS level interrupt merge)

| 寄存器 | 接入类型 | 描述 |

|---|---|---|

| MASK | RW | 整形mask寄存器, 1:关闭; 0: 打开;默认1关闭 |

| STATUS | RO | 整形状态, RO, status = int_level && ! mask |

Spinal使用:

busif.interruptLevelFactory("T", sys_int0, sys_int1)

三、Spinal库(Spinal Factory)

| 总线接口方法 | 描述 |

|---|---|

InterruptFactory(regNamePre: String, triggers: Bool*) |

为脉冲事例创造RAW/FORCE/MASK/STATUS |

InterruptFactoryNoForce(regNamePre: String, triggers: Bool*) |

为脉冲事例创造RAW/MASK/STATUS |

InterruptFactory(regNamePre: String, triggers: Bool*) |

为level_int合并创建MASK/STATUS |

InterruptFactoryAt(addrOffset: Int, regNamePre: String, triggers: Bool*) |

为在adderOffset的脉冲事例创建RAW/FORCE/MASK/STATUS |

InterruptFactoryNoForceAt(addrOffset: Int, regNamePre: String, triggers: Bool*) |

为在adderOffset的脉冲事例创建RAW/MASK/STATUS |

InterruptFactoryAt(addrOffset: Int, regNamePre: String, triggers: Bool*) |

为在adderOffset的level_int合并MASK/STATUS |

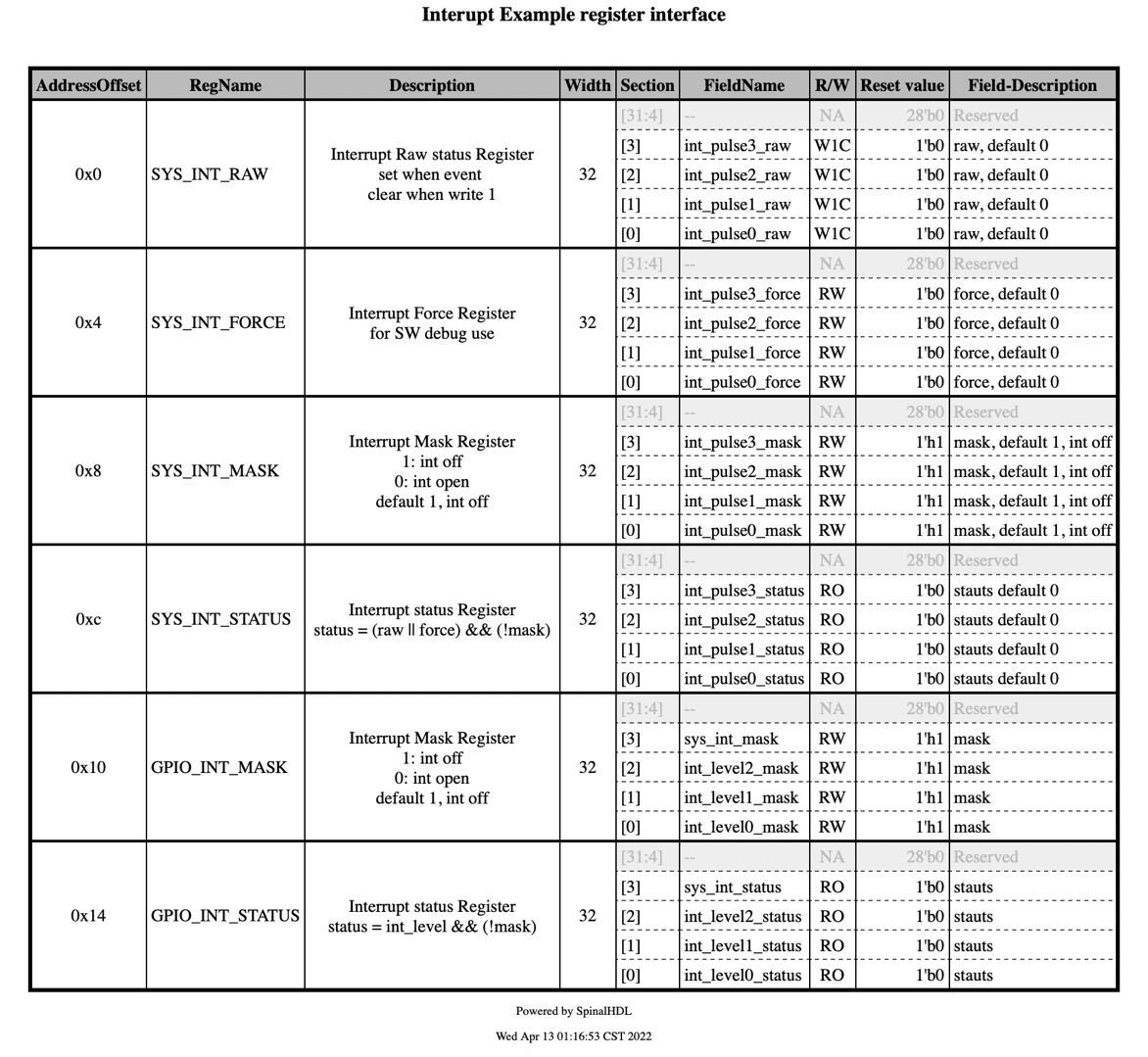

四、例子(Example)

class RegFileIntrExample extends Component{

val io = new Bundle{

val apb = slave(Apb3(Apb3Config(16,32)))

val int_pulse0, int_pulse1, int_pulse2, int_pulse3 = in Bool()

val int_level0, int_level1, int_level2 = in Bool()

val sys_int = out Bool()

val gpio_int = out Bool()

}

val busif = BusInterface(io.apb, (0x000,1 KiB), 0, regPre = "AP")

io.sys_int := busif.interruptFactory("SYS",io.int_pulse0, io.int_pulse1, io.int_pulse2, io.int_pulse3)

io.gpio_int := busif.interruptLevelFactory("GPIO",io.int_level0, io.int_level1, io.int_level2, io.sys_int)

def genDoc() = {

busif.accept(CHeaderGenerator("intrreg","Intr"))

busif.accept(HtmlGenerator("intrreg", "Interupt Example"))

busif.accept(JsonGenerator("intrreg"))

this

}

this.genDoc()

}

五、开发区域(Developers Area)

用户可以通过扩展BusIfVistor Trait来添加用户的文档类型。

case class Latex(fileName : String) extends BusIfVisitor{ ... }

BusIfVistor提供对BusIf.RegInsts的访问来实现用户所需的:

// lib/src/main/scala/lib/bus/regif/BusIfVistor.scala

trait BusIfVisitor {

def begin(busDataWidth : Int) : Unit

def visit(descr : FifoDescr) : Unit

def visit(descr : RegDescr) : Unit

def end() : Unit

}